# MN39243FT

## 6 mm (type-1/3) High-sensitivity CCD Area Image Sensor

#### Overview

The MN39243FT is a 6 mm (type-1/3) interline transfer CCD (IT-CCD) solid state image sensor device.

This device uses photodiodes in the optoelectric conversion section and CCDs for signal readout. The electronic shutter function has made an exposure time of 1/10 000 seconds possible. Further, this device has the features of high sensitivity, low noise, broad dynamic range, and super-low smear.

This device has a total of 466032 pixels (798 horizontal  $\times$  584 vertical) and provides stable and clear images with a resolution of 480 horizontal TV-lines and 420 vertical TV-lines.

| Part Number | Size            | System | Color or B/W |

|-------------|-----------------|--------|--------------|

| MN39243FT   | 6 mm (type-1/3) | PAL    | Color        |

#### Features

- Total number of pixels: 798 (horizontal) × 584 (vertical)

- High sensitivity

- Broad dynamic range (compared to our conventional CCD ×1.2)

- Low smear

- Electronic shutter

- No image distortion

- Small size enables design of compact equipment

- High reliability

#### Applications

• Camcorders, surveillance cameras, door cameras

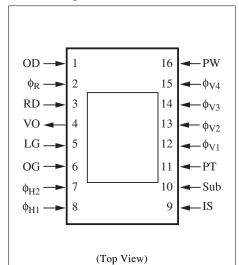

#### Pin Assignments

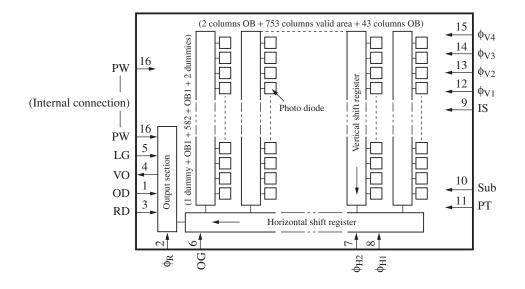

### Block Diagram

#### Pin Descriptions

| Pin No. | Symbol                 | Description                       | Pin No. | Symbol          | Description                           |

|---------|------------------------|-----------------------------------|---------|-----------------|---------------------------------------|

| 1       | OD                     | Output drain                      | 9       | IS              | Horizontal CCD input source           |

| 2       | φ <sub>R</sub>         | Reset pulse                       | 10      | Sub             | Substrate                             |

| 3       | RD                     | Reset drain                       | 11      | РТ              | P-well for protection circuit         |

| 4       | VO                     | Video output                      | 12      | $\phi_{V1}$     | Vertical shift register clock pulse 1 |

| 5       | LG                     | Output load transistor gate       | 13      | $\phi_{V2}$     | Vertical shift register clock pulse 2 |

| 6       | OG                     | Output gate                       | 14      | φ <sub>V3</sub> | Vertical shift register clock pulse 3 |

| 7       | <b>ф</b> <sub>Н2</sub> | Horizontal register clock pulse 2 | 15      | $\phi_{\rm V4}$ | Vertical shift register clock pulse 4 |

| 8       | $\phi_{\rm H1}$        | Horizontal register clock pulse 1 | 16      | PW              | P-well                                |

## ■ Absolute Maximum Ratings and Operating Conditions

| Parameter                           |                                     |                                            | Rating            |      | Operating condition |      |        |      |

|-------------------------------------|-------------------------------------|--------------------------------------------|-------------------|------|---------------------|------|--------|------|

|                                     |                                     | Symbol                                     | Min               | Max  | Min                 | Тур  | Max    | Unit |

| Reset drain voltage                 | e                                   | V <sub>RD</sub>                            | - 0.2             | 18.0 | 14.5                | 15.0 | 15.5   | V    |

| Output drain volta                  | ge                                  | V <sub>OD</sub>                            | - 0.2             | 18.0 | 14.5                | 15.0 | 15.5   | V    |

| Output load transis<br>gate voltage | stor                                | V <sub>LG</sub>                            | (Internal bias)   |      |                     |      |        |      |

| Output gate voltag                  | e                                   | V <sub>OG</sub>                            | (Internal bias)   |      |                     |      |        |      |

| Horizontal CCD input                | source voltage                      | V <sub>IS</sub>                            | - 0.2             | 18.0 | 14.5                | 15.0 | 15.5   | V    |

| Protection P-well                   | voltage                             | V <sub>PT</sub> * <sup>3, 4</sup>          | -9.0              | 0.2  | -7.3                | -7.0 | -6.7   | V    |

| P-well voltage                      |                                     | $V_{\rm PW}$                               | Reference voltage |      |                     | 0    |        | V    |

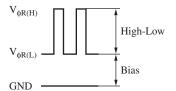

| Reset                               | High-Low                            | $V_{\phi R(H-L)}$ *1                       | _                 | 5.0  | 3.0                 | 3.3  | 3.6    | V    |

| pulse voltage                       | Bias                                | V <sub>\$\$R(Bias)</sub> *1                |                   |      | Supplied internally |      |        | V    |

| Horizontal register                 |                                     | V <sub>\$\phi H1(H)</sub>                  | _                 | 5.0  | 3.0                 | 3.3  | 3.6    | V    |

| clock pulse voltage 1               |                                     | V <sub>\u0066H1(L)</sub>                   | - 0.2             |      | - 0.1               | 0    | 0.1    | 1    |

| Horizontal register                 |                                     | $V_{\phi H2(H)}$                           | _                 | 5.0  | 3.0                 | 3.3  | 3.6    | V    |

| clock pulse voltage 2               |                                     | V <sub>\operatorname{H2(L)}</sub>          | - 0.2             |      | - 0.1               | 0    | 0.1    |      |

| Vertical shift register             |                                     | V <sub>\$\phiV1(H)</sub> *3, 4             | _                 | 18.0 | 14.5                | 15.0 | 15.5   | V    |

| clock pulse voltage 1               |                                     | V <sub>\$\phiV1(M)</sub> *3, 4             | _                 |      | - 0.2               | 0    | 0.2    |      |

|                                     |                                     | V <sub>\$\phiV1(L)</sub> *3, 4             | -9.0              |      | -7.3                | -7.0 | -6.7   |      |

| Vertical shift register             |                                     | V <sub>\$\phiV2(M)</sub> *3, 4             |                   | 15.0 | - 0.2               | 0    | 0.2    | V    |

| clock pulse voltage                 | e 2                                 | V <sub>\$\phiV2(L)</sub> *3, 4             | -9.0              |      | -7.3                | -7.0 | ) –6.7 |      |

| Vertical shift register             |                                     | V <sub>\$\phiV3(H)</sub> *3, 4             | _                 | 18.0 | 14.5                | 15.0 | 15.5   | V    |

| clock pulse voltage 3               |                                     | c pulse voltage 3 $V_{\phi V3(M)}^{*3, 4}$ |                   |      | - 0.2               | 0    | 0.2    |      |

|                                     |                                     | V <sub>\$\phiV3(L)</sub> *3, 4             | -9.0              |      | -7.3                | -7.0 | -6.7   |      |

| Vertical shift register             |                                     | V <sub>\$\phiV4(M)</sub> *3, 4             | _                 | 15.0 | - 0.2               | 0    | 0.2    | V    |

| clock pulse voltage 4               |                                     | $V_{\phi V4(L)} *3, 4$                     | -9.0              |      | -7.3                | -7.0 | -6.7   | 1    |

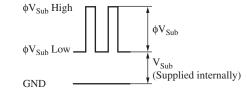

| Substrate voltage                   |                                     | V <sub>Sub</sub> *2                        | - 0.2 45.0        |      | Supplied internally |      |        | V    |

|                                     |                                     | $\phi V_{Sub} *^2$                         | ]                 |      | 21.0                | 22.0 | 23.0   |      |

| Operating tempera                   | rating temperature T <sub>opr</sub> |                                            |                   | 70   |                     | 25   |        | °C   |

| Storage temperatur                  | re                                  | T <sub>stg</sub>                           | -30               | 80   |                     |      |        | °C   |

Note) \*1: Reset

\*2:  $V_{Sub}$  when using electronic shutter function

\*3: Absolute maximum rating  $-0.2 < V_{\phi V} - V_{PT} < 24.5 (V)$

\*4: Relation between  $V_{PT}$  and  $V_{\varphi V(L)}$

Set  $V_{PT}$  that is to meet the following conditions for VL voltage of the vertical shift clock waveform.  $V_{PT} \leq VL (V_{\phi V1(L)} \text{ to } V_{\phi V4(L)})$

## Optical Characteristics

| Part Number | Color<br>or | Effective Saturation<br>pixels output |     | Sensitivity<br>F8 | Vertical smear<br>Sm | Horizontal resolution | Vertical resolution |                |

|-------------|-------------|---------------------------------------|-----|-------------------|----------------------|-----------------------|---------------------|----------------|

|             | B/W         | H                                     | V   | Typ (mV)          | Typ (mV)             | Typ (dB)              |                     | Typ (TV-lines) |

| MN39243FT   | Color       | 737                                   | 575 | 750               | 450                  | -100                  | 480                 | 420            |

## ■ Graph of Characteristics

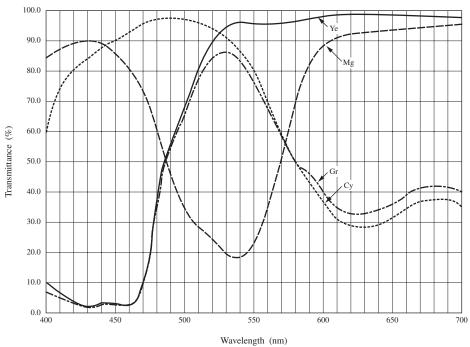

#### CCD color filter spectral characteristics

### ■ Timing Diagram

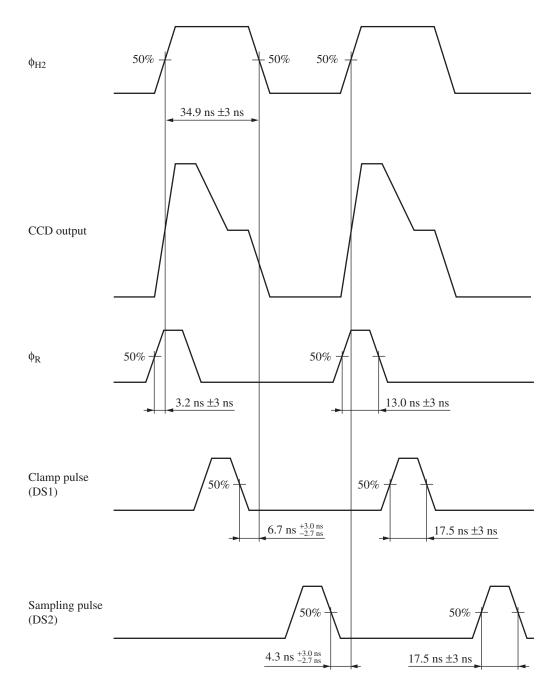

• High speed pulse timing

#### Timing Diagram (continued)

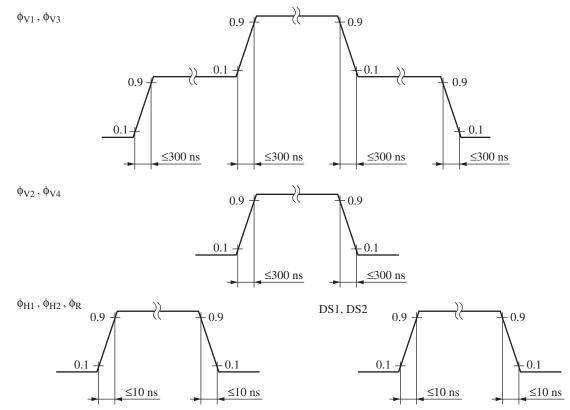

• Rise time and fall time of each pulse

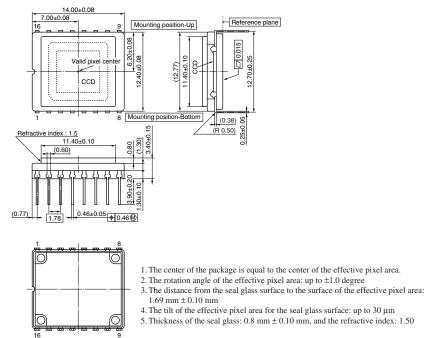

- Package Dimensions (unit: mm)

- WDIP016-P-0500C

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

#### Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.